Tugas Pendahuluan 1 Modul 2

By: Rahmad Fajril Ilhami

2210951016

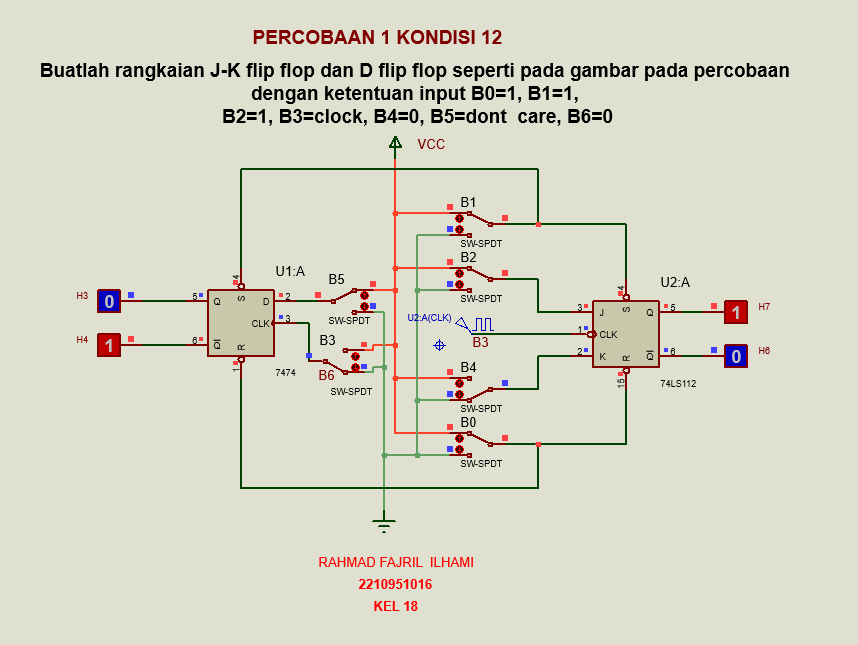

Percobaan 1 Kondisi 12

1. Kondisi [Kembali]

2. Rangkaian Simulasi [Kembali]

Berdasarkan gambar rangkaian sebelumnya, diketahui prinsip kerjanya adalah sebagai berikut

D-Flip Flop

Awalnya kita perlu melihat inputan dari IC 7474 tersebut dimana B1 terhubung dengan VCC sehingga mengalirkan arus berlogika 1 ke pin S. B0 di sini terhubung dengan ground sehingga input dari pin R adalah logika 0. Untuk pin D tidak dihubungkan serta pin CLK dihubungkan dengan inputan Clock. Terlihat di IC 7474 bahwa terdapat bulatan kecil pada pin RS sehingga dapat disimpulkan bahwa pin RS bersifat aktif low atau akan aktif jika inputannya logika nol (rendah), sebaliknya jika inputannya logika 1 (tinggi) maka tidak aktif. Karena salah satu Pin RS berlogika 1 maka inputan lain seperti pin D dan Clock tidak dihiraukan atau diabaikan yang menandakan RS aktif. Pin S menerima input logika 0 sehingga pin S aktif, sedangkan pin R menerima input logika 1 sehingga pin R tidak aktif yang menyebabkan kondisi set. Sesuai tabel kebenaran RS- Flip flop saat S aktif atau sama dengan 1 dan R sama dengan nol maka outputnya adalah Q=1 dan Q' adalah kebalikan dari Q yaitu 0.

JK-Flip Flop

Awalnya kita perlu melihat inputan dari IC 74LS112 dimana B1 terhubung dengan VCC sehingga mengalirkan arus berlogika 1 ke pin S. B0 di sini terhubung dengan ground sehingga input dari pin R adalah logika 0. B2 terhubung dengan VCC sehingga input pin J berlogika 1. B4 terhubung dengan VCC sehingga input pin K berlogika 1. Pin CLK terhubung dengan inputan clock. Dalam kondisi ini pin S menerima input logika 0 sehingga pin S aktif, sedangkan pin R menerima input logika 1 sehingga pin R tidak aktif. Jadi kondisi flip flop adalah set dimana S=1 dan R=0. Dikarenkan RS aktif, maka inputan lain seperti J,CLK, dan K tidak dianggap. Sesuai tabel kebenaran RS-Flip Flop saat S=1 dan R=0 maka Q=1 dan Q' kebalikannya yaitu 0.

Komentar

Posting Komentar