Laporan Akhir 1 Modul 2

By: Rahmad Fajril Ilhami

2210951016

Laporan Akhir 1

(Percobaan 1)

2. Alat dan Bahan [Kembali]

Percobaan 1 J-K flip flop dan D flip flop

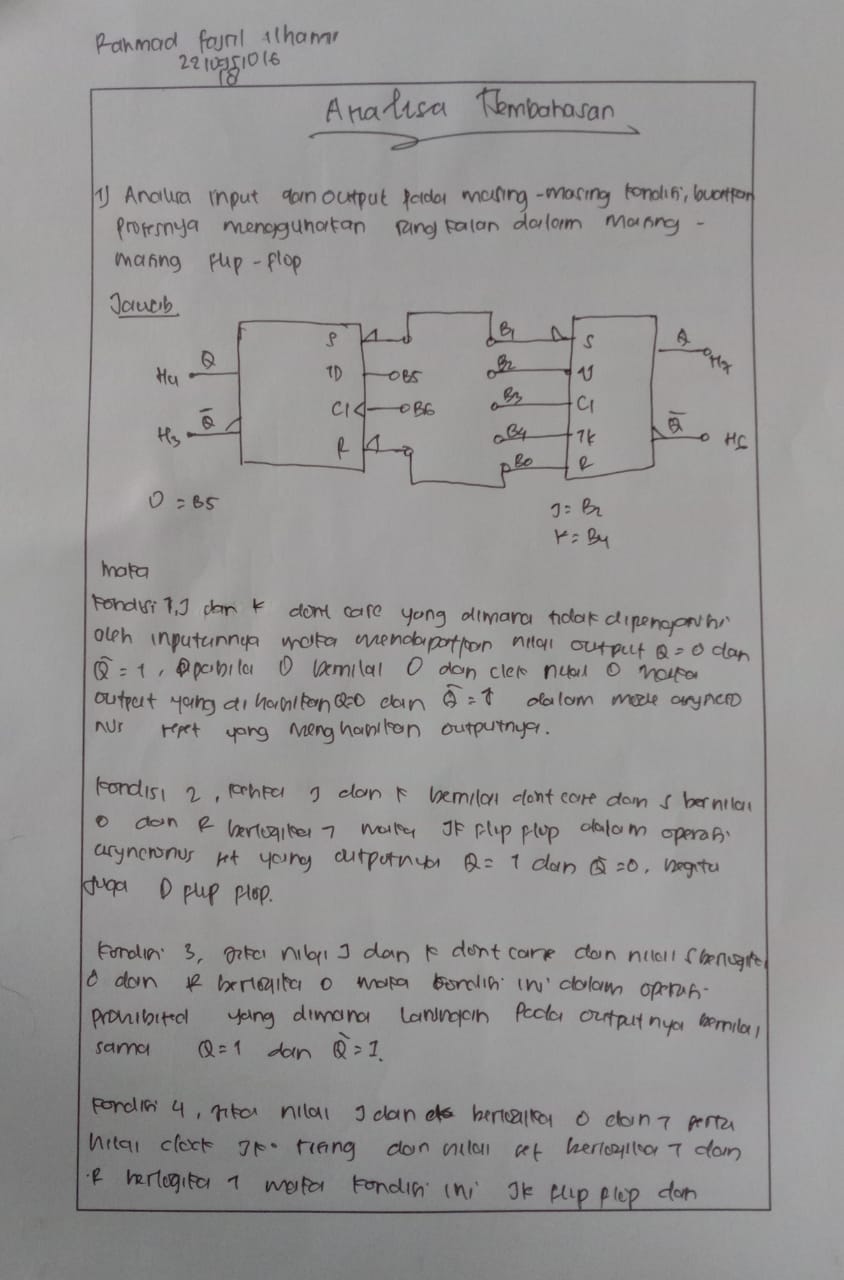

1. Buatlah rangkaian seperti pada gambar berikut.

2. Buatlah kondisi switch-switch seperti pada jurnal yang telah disediakan

3. Catat kondisi logika LED H0 & H1 nya.

4. Prinsip Kerja Rangkaian [Kembali]

1. Pada kondisi 1, dengan kondisi B0 = 0 ; B1 = 1 ; B2 = B3 = B4 = B5 = B6 = don't care. Maka didapatkan output untuk JK Flip-Flop berupa Q = 0, Q' = 1, di dilihat pada percobaan, kaki B0 terhubung dengan Reset (R) dan kaki B1 terhubung dengan Set (S), yang mana sama-sama aktif low maka reset akan aktif karena berlogika 0 dan akan memaksa output Q untuk bernilai 0. Selanjutnya untuk output D Flip-Flop, untuk mengaktifkan set reset pada D flip-flop diharuskan bernilai 0 karena aktif low. Karena riset aktif, maka ia memaksa output untuk bernilai 0.

2. Untuk kondisi 2, dengan kondisi B0 = 1; B1 = 0; B2 = B3 = B4 = B5 = B6 = dont care maka didapatkan output dari JK flip-flop Q = 1; Q' = 0 dan output D Flip-Flop Q = 1; Q' = 0 hal tersebut dikarenakan arus yang masuk pada set reset; S = 0; R = 1 dimana set reset merupakan aktif low yang mana akan aktif saat berlogika 0 maka dari itu set aktif dan akan memaksa nilai Q' untuk bernilai 0 atau saat reset tidak aktif, ia akan memaksa output untuk logika 1.

3. Untuk kondisi 3, dengan kondisi B0 = 0; B1 = 0; B2 = B3 = B4 = B5 = B6 = dont care didapatkan output JK Flip-Flop Q = 1 ; Q' = 1 dan output D Flipo-Flop Q = 1; Q' = 1 maka terjadi kondisi terlarang atau keadaan yang tidak diperbolehkan.

4. Untuk kondisi 4, dengan kondisi B0 = 1; B1 = 1; B2 = 0; B3 = clock; B4 = 0 ; B5 = 0 ; B6 = 1 didapatkan output JK Flip-Flop Q = 0; Q' = 1 dan D Flip-Flop dengan output Q = 0 ; Q' = 1 hal tersebut terjadi karena set reset tidak aktif dikarenakan aktif flow, sehingga untuk JK Flip Flop memperoleh input dari J, K, clock begitu juga input D flip flop dari D dan clock.

5. Untuk kondisi 5, dengan kondisi B0 = 1; B1 = 1; B2 = 0; B3 = clock; B4 = 1; B5 = 1; B 6 = mengikuti output sebelumnya. Dihasilkan output JK Flip Flop berupa Q = 0; Q' = 1 dan D Flip Flop berupa Q = 0; Q' = 1 dikarenakan saat reset tidak aktif karena berlogika 1 maka output dipengaruhi oleh nilai J, K, D, dan clock-nya untuk outputnya sesuai dengan tabel kebenaran.

6. Untuk kondisi 6, dengan kondisi B0 = 1; B1 = 1; B2 = 1; B3 = clock; B4 = 0; B5 dont care; B6 = 0, didapatkan output JK Flip Flop Q = 1; Q' = 0 dan output D Flip-Flop berupa Q = 0; Q' = 1 maka karena set reset aktif low dan tidak aktif maka kita mengikuti nilai J, K, D, clock dan menyamakannya dengan tabel kebenaran.

7. Untuk kondisi 7 di mana B0 = 1; B1 = 1; B2 = 1; B3 = clock; B4 = 1; B5 = B6 = tidak ada, didapatkan output dari JK Flip Flop Q = toggle; Q' = toggle dan output dari D Flip-Flop tidak ada, hal tersebut dikarenakan output dari JK Flip Flop akan berkebalikan secara terus-menerus.

5. Video Rangkaian [Kembali]

Komentar

Posting Komentar